“port_1″の表示が2進数表記になっているので10進数表記に変更してみます。”port_1″を選択して右クリックすると以下のようなメニューが表示されるので、「Radix」->「Unsigned Decimal」を選択します。

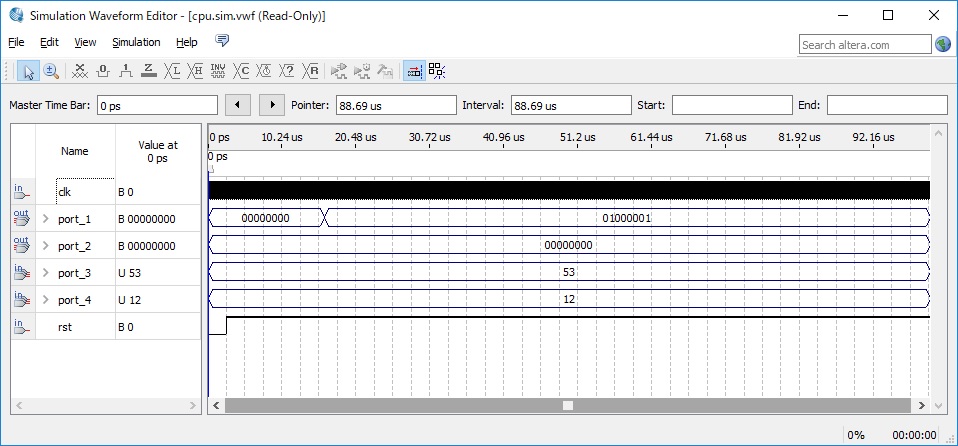

以下のように”port_1″の表示が10進数表記に変更されました。表示された”port_1″の出力値は”65″なので、53+12の答えが正常に出力されていることが分かります。

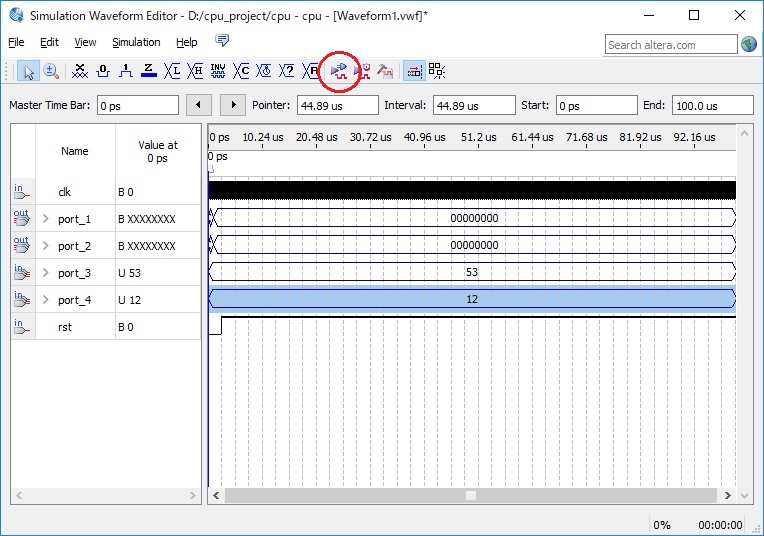

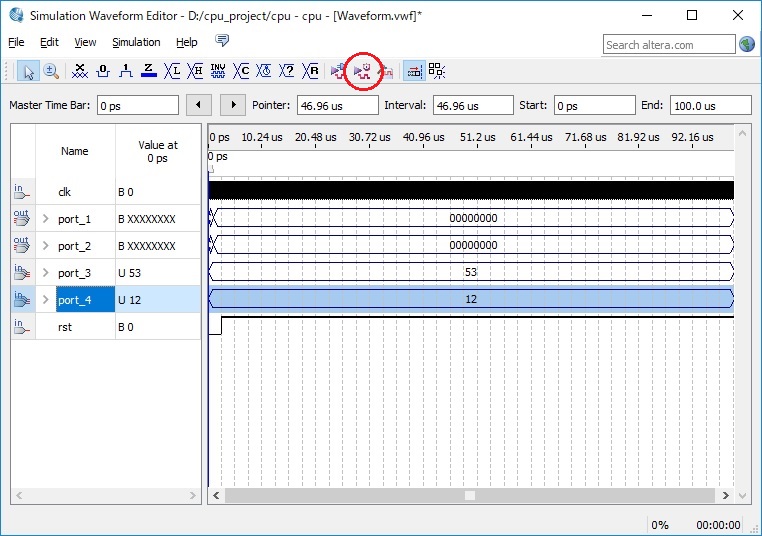

上記の方法は機能的な部分を確認するためのシミュレーションですので、実際の回路で発生する信号の遅延などは考慮されていません。信号の遅延なども含めて確認を行う場合は以下の”Run Timing Simulation”ボタンの方を使用します。