ピンプランナーで使用されなかったピンの動作はQuartusの設定によって異なります。未使用ピンの設定によっては外部回路との接続に問題が生じる可能性があるので念のために確認しておくのが良いでしょう。

以下の手順で未使用ピンの設定が確認できます。

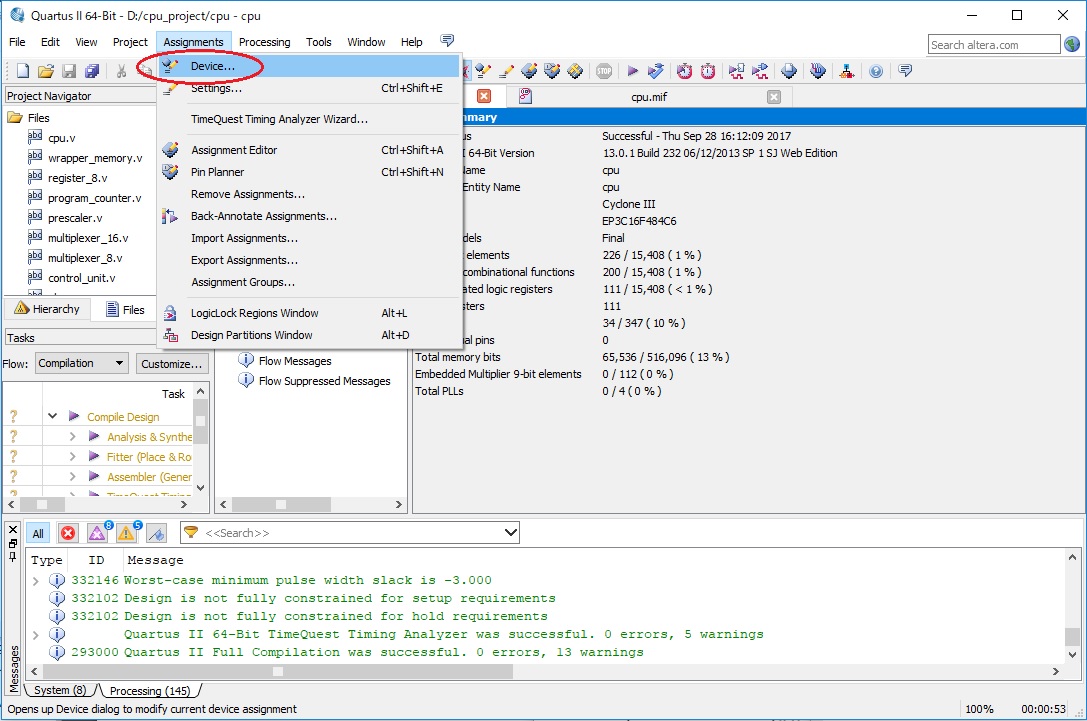

Quartusのメニューから「Assignments」->「Device…」を選択します。

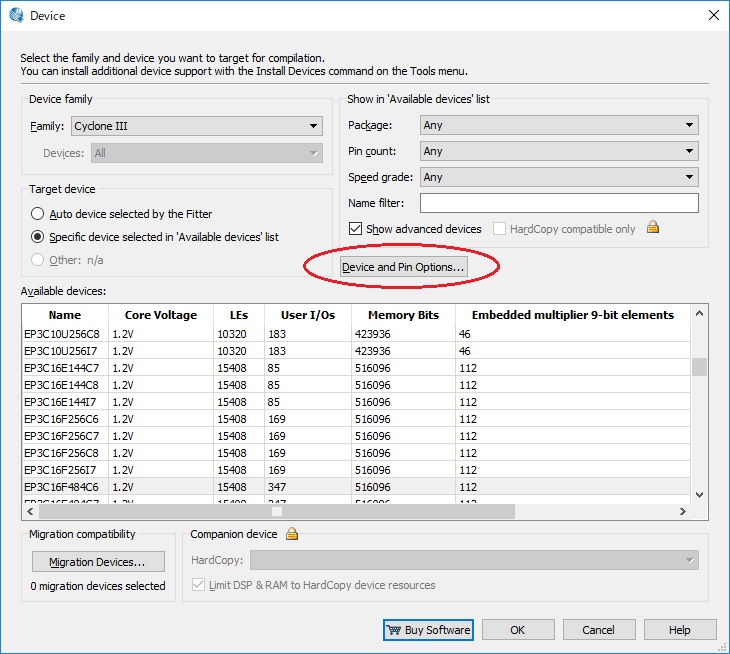

“Device and Pin Options…”を押します。

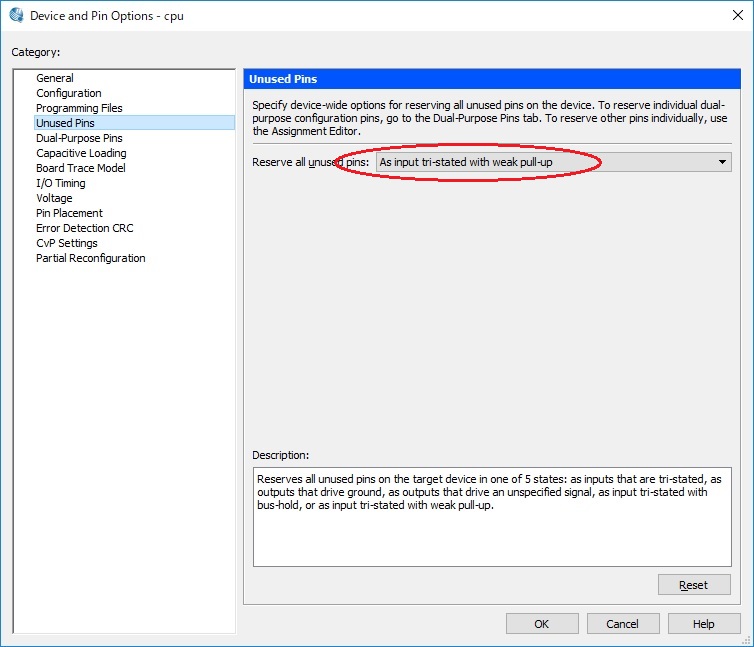

以下の画面が表示されますので、左側の”Category:”欄から”Unused Pins”を選択します。

“Unused Pins”の設定が表示されます。

未使用ピンの設定として、特定の電圧が出力されるような状態は場合によっては問題が生じることがあります。具体的には未使用ピンがGNDに設定されている場合などに、外部回路からその未使用ピンへ電源が接続されていたりするとデバイスがショートしてしまうようなことが考えられます。比較的に安全と思われる設定は以下の”As input tri-stated with weak pull-up”などの設定です。