ここからはQuartusを使ってメモリ回路を作成する方法を紹介していきます。自作CPUをFPGA上で動かすにはプログラムを書き込むためのメモリ回路を用意する必要があります。AlteraのFPGAには内部にメモリ回路を作成するための専用の記憶領域があり、Quartusの「MegaWizard Plug-In Manager」というツールを使ってこの領域にメモリ回路を作成することができます。

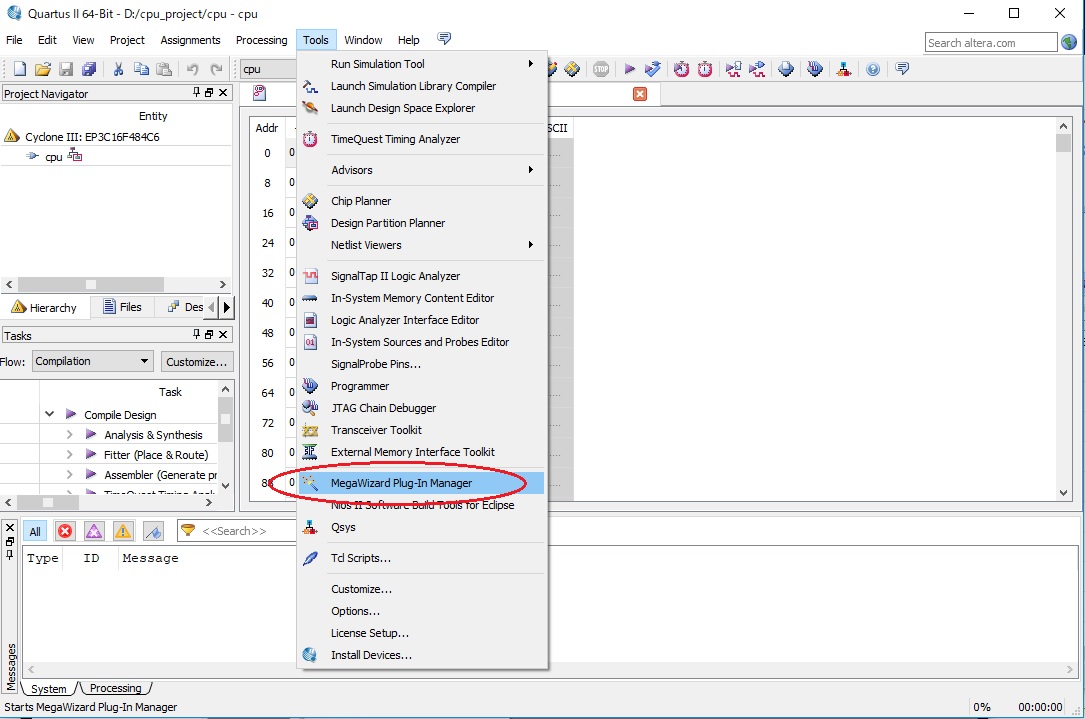

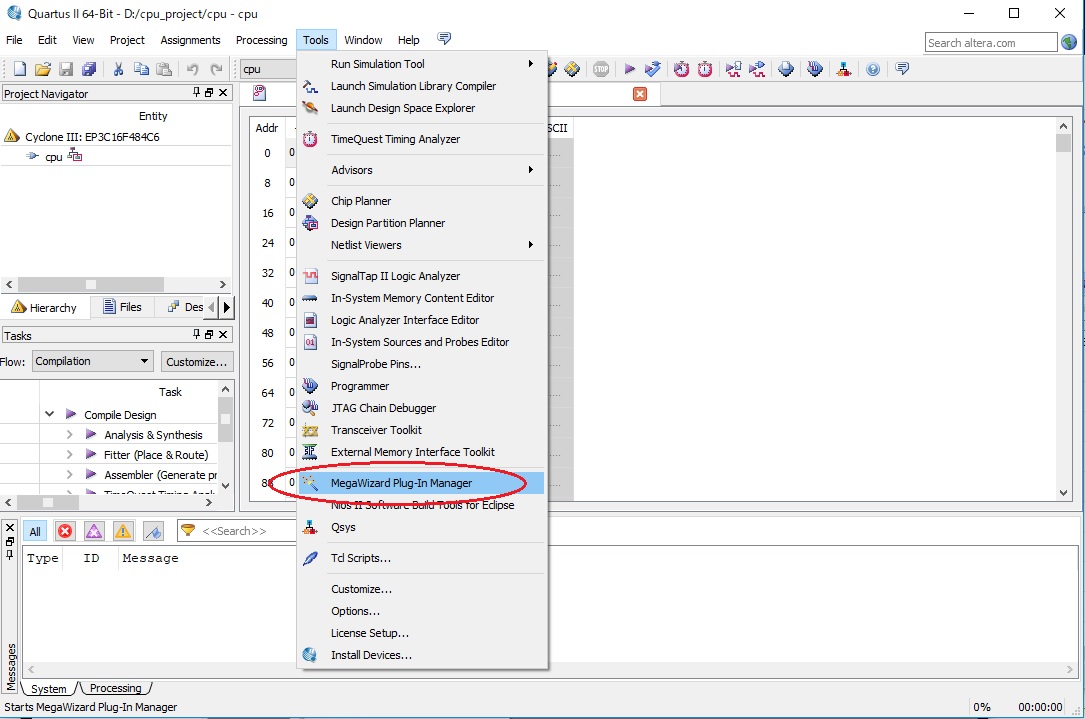

まずQuartusのメニューから「Tools」->「MegaWizard Plug-In Manager」を選択します。

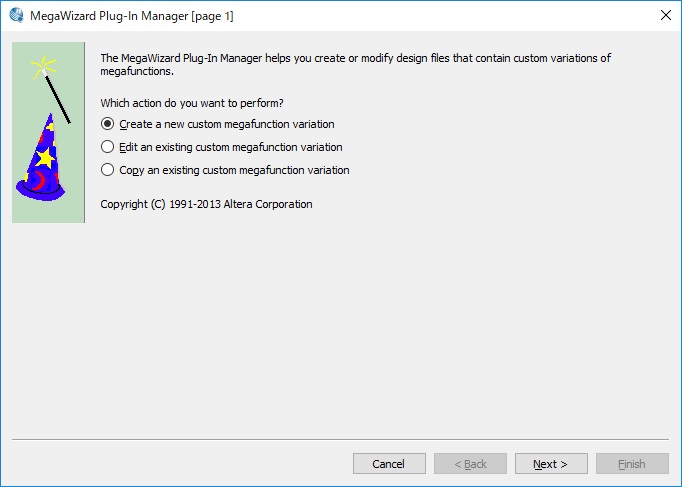

以下の画面が表示されるので”Next”を押します。

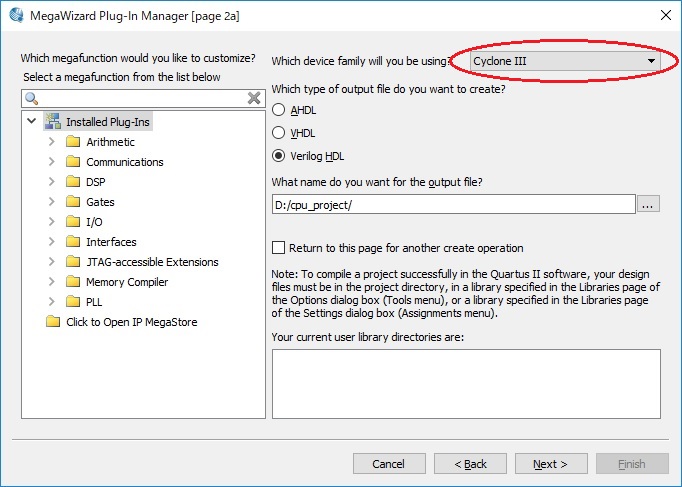

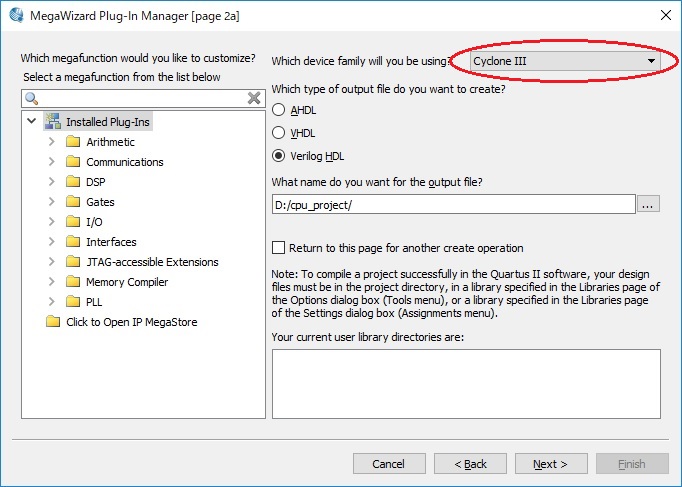

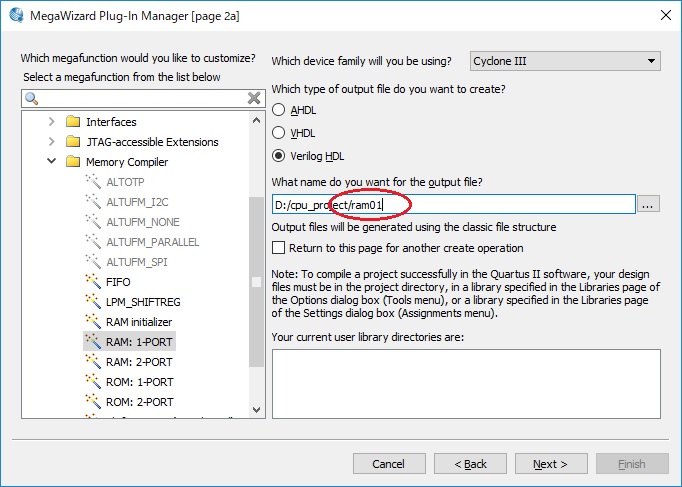

以下の画面が表示されたら使用するFPGAのデバイスファミリを選択します。

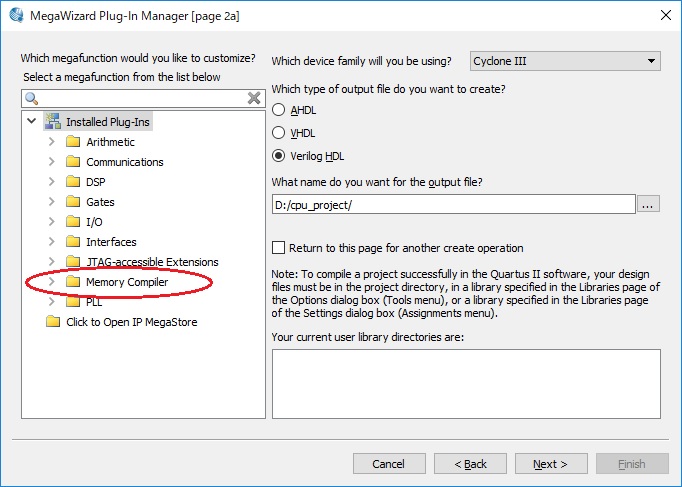

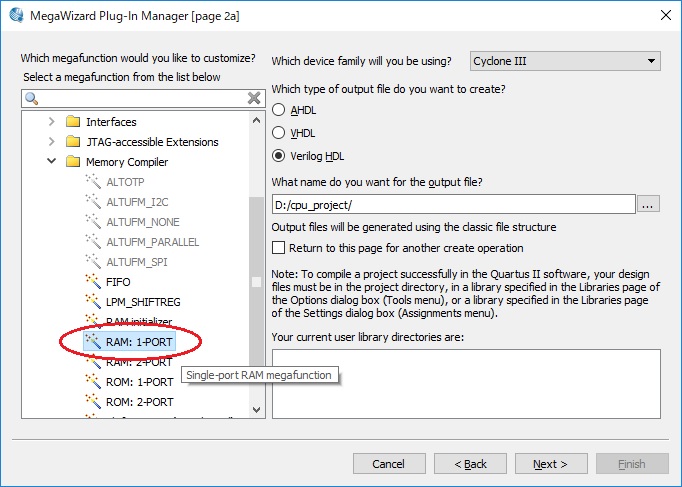

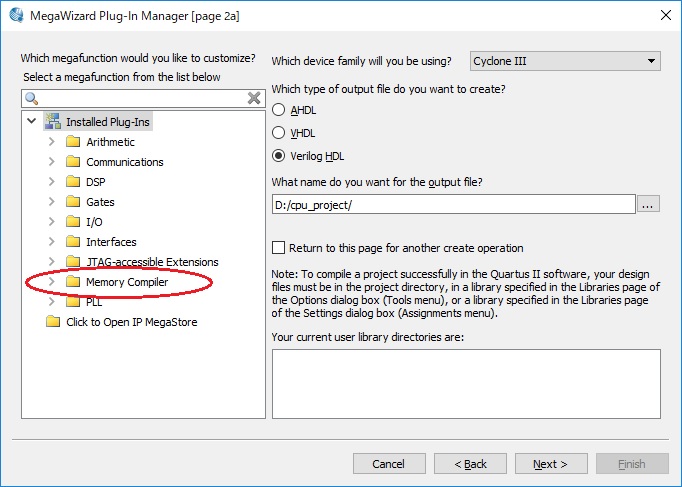

デバイスファミリを選択した後、以下の印を付けた場所に表示されている”Memory Compiler”を開きます。

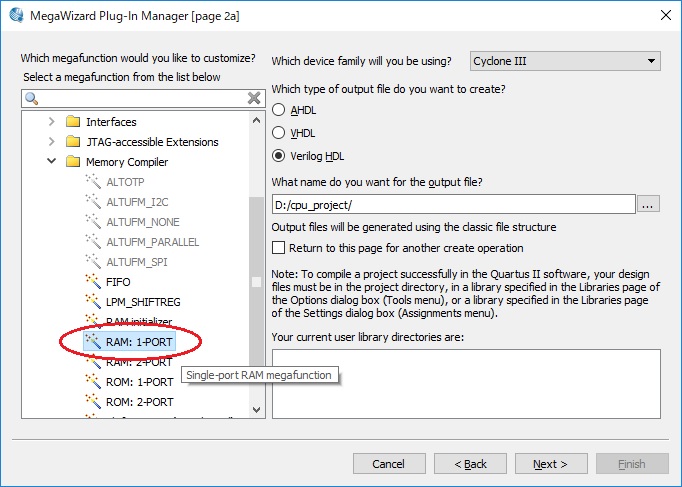

“Memory Compiler”を開くといろいろな記憶回路が表示されますので、その中から”RAM: 1-PORT”を選択します。

以下の印を付けた箇所には使用する言語を選択するボタンがあります。今回作成するCPUのコードはVerilog HDLで書かれているので”Verilog HDL”にチェックを入れます。

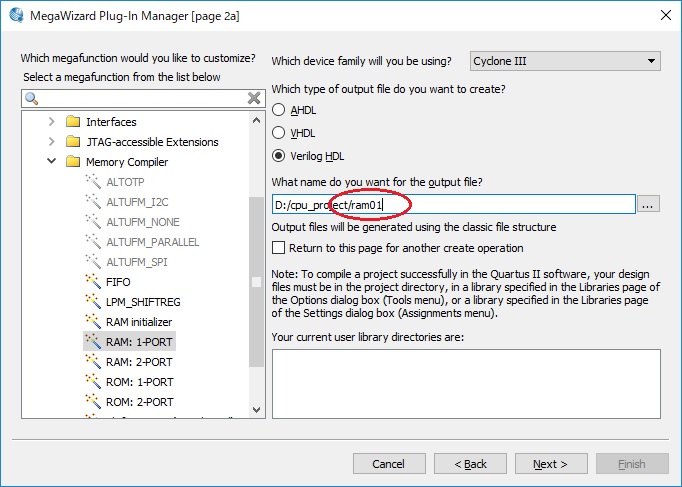

以下の画面では印がついてある箇所にこれから作成するメモリ回路の出力先ファイルパスを入力します。ここではプロジェクト作成時に用意した作業用フォルダの直下に”ram01″という名前を追加しています。この名前はメモリ回路のファイル名になると同時にVerilog HDLから呼び出す際のモジュール名にもなりますので今回作成するCPUのソースコードをそのまま使用する場合は、ここで入力する名前を”ram01″としてください。名前の入力が完了したら”Next”を押します。

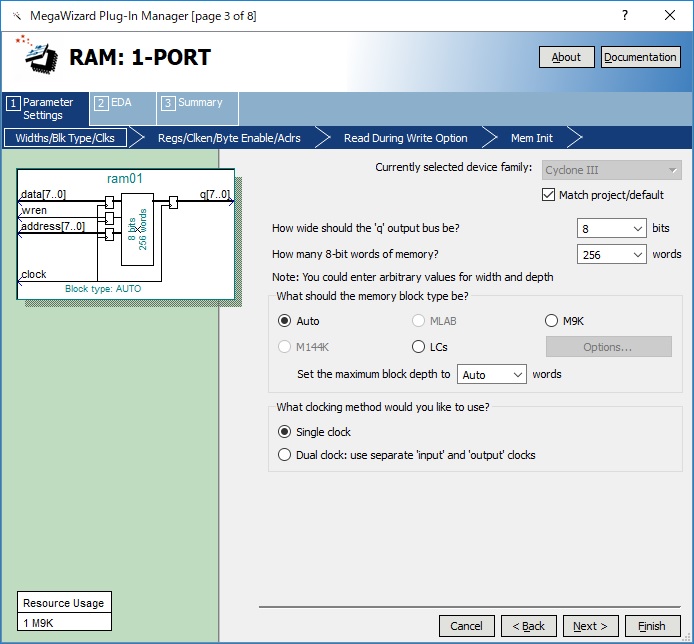

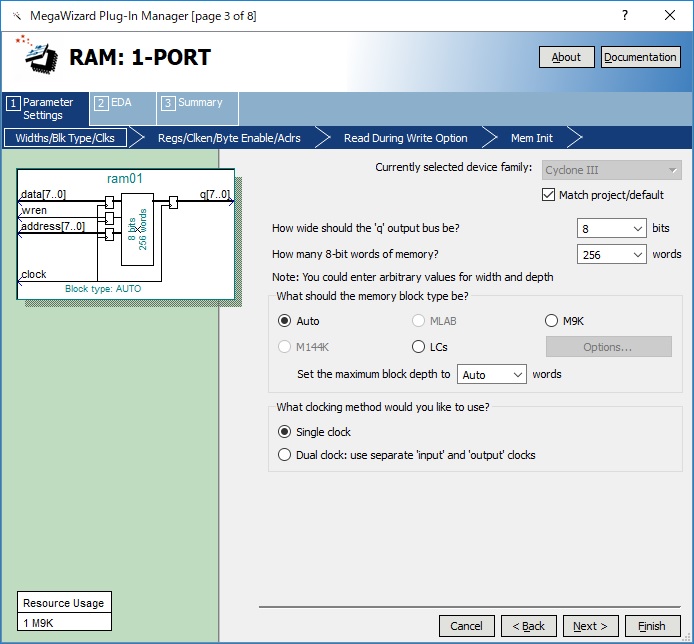

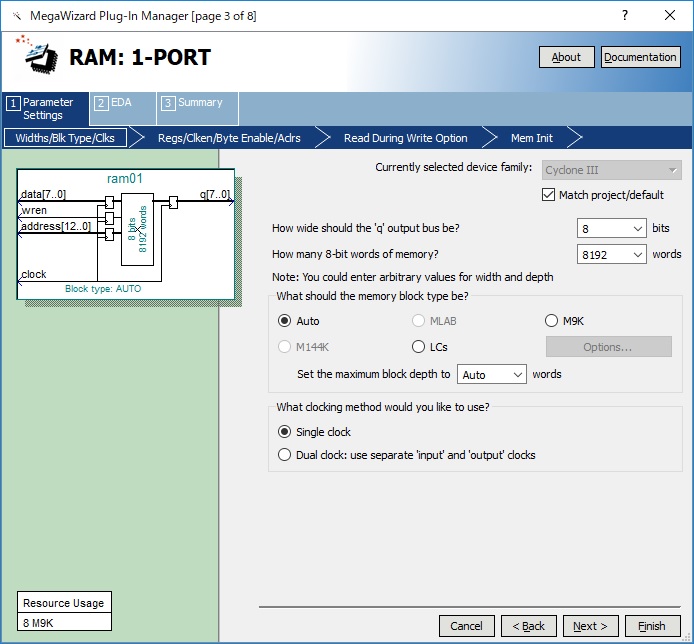

ここからは作成するRAM回路の仕様を決めていきます。設定する項目は主にビット数と番地数、RAMの初期化に用いるMIFファイルです。MIFファイルは前ページで作成した”cpu.mif”を使用します。またビット数と番地数も前ページで作成した”cpu.mif”ファイルの設定に合わせてビット数は「8」、番地数は「8192」とします。

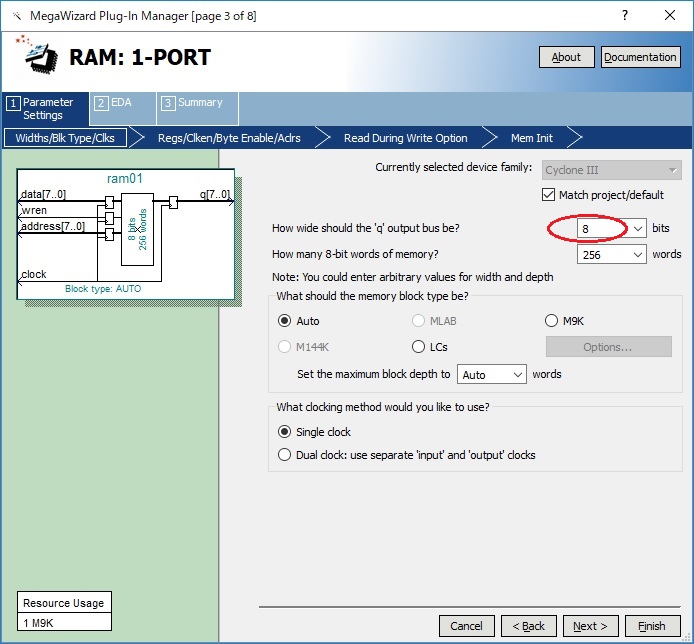

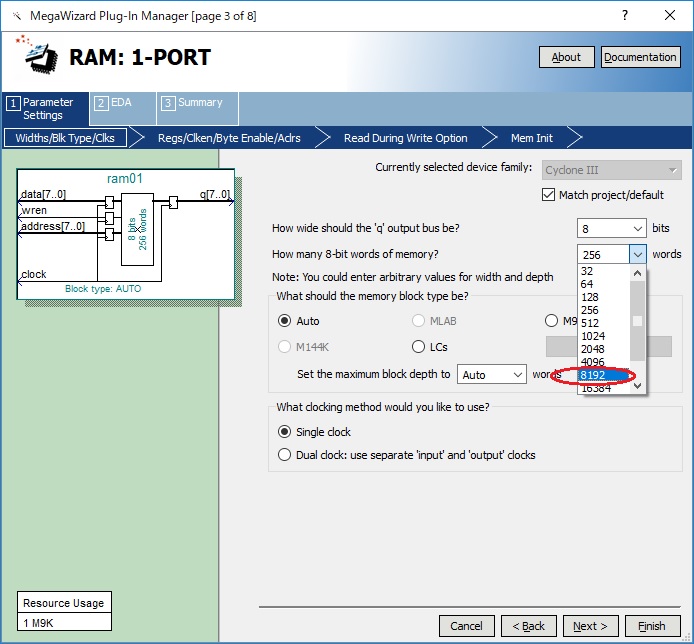

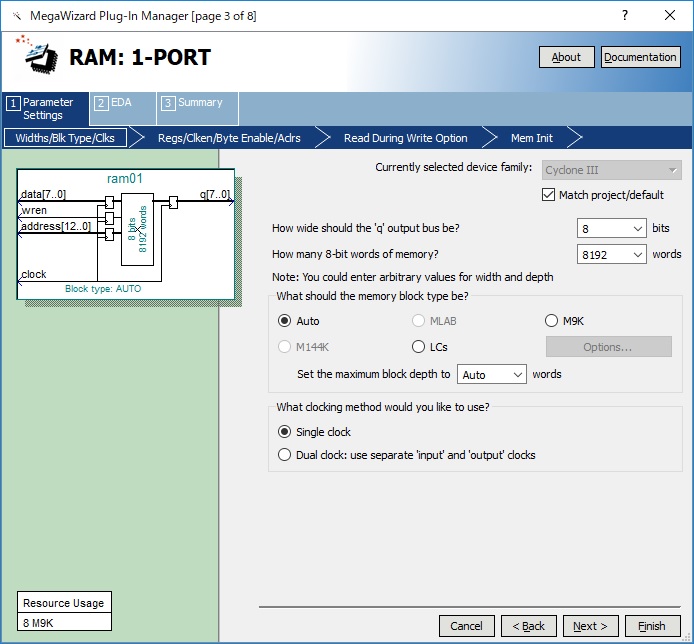

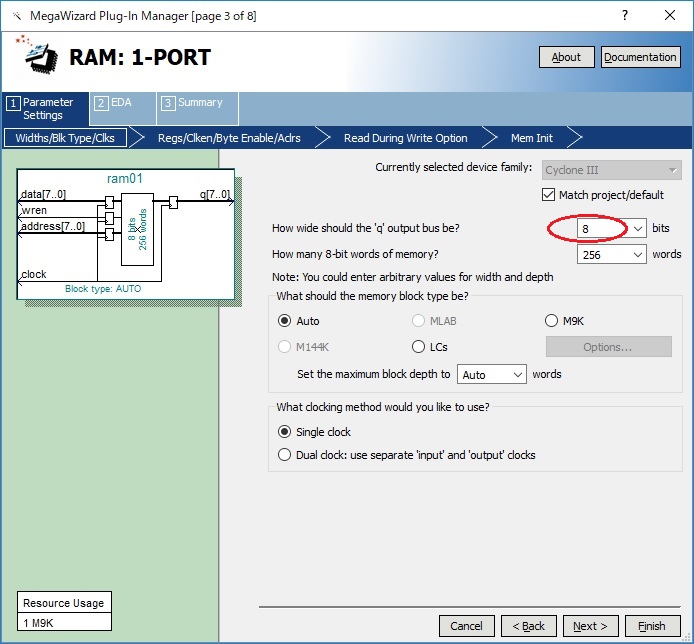

RAM回路のビット数は以下の印の箇所に設定します。設定する値は「8」とします。

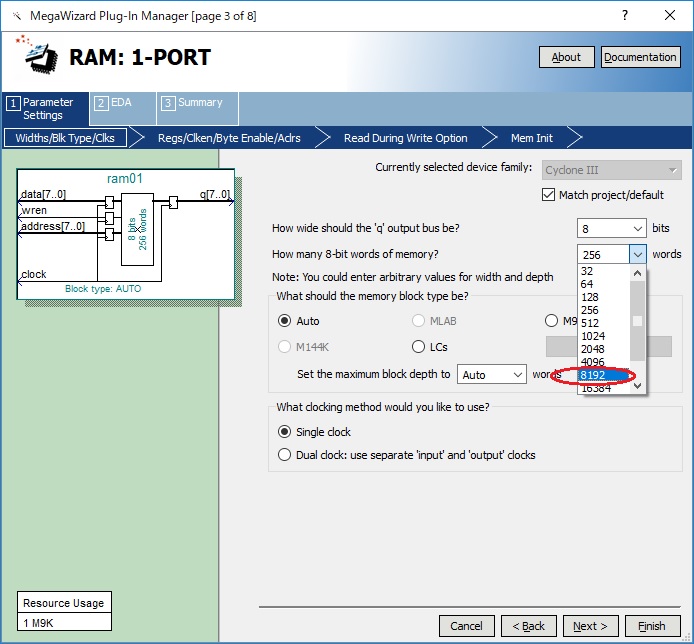

RAM回路の番地数は以下の印の箇所に設定します。設定する値は「8192」とします。(ここで番地数を8192に設定するということは13ビットのアドレス入力端子を持つRAM回路を作成するということを意味しています。)

他の箇所は初期値のままで良いですので以下のように設定できたら”Next”を押します。

スポンサーリンク

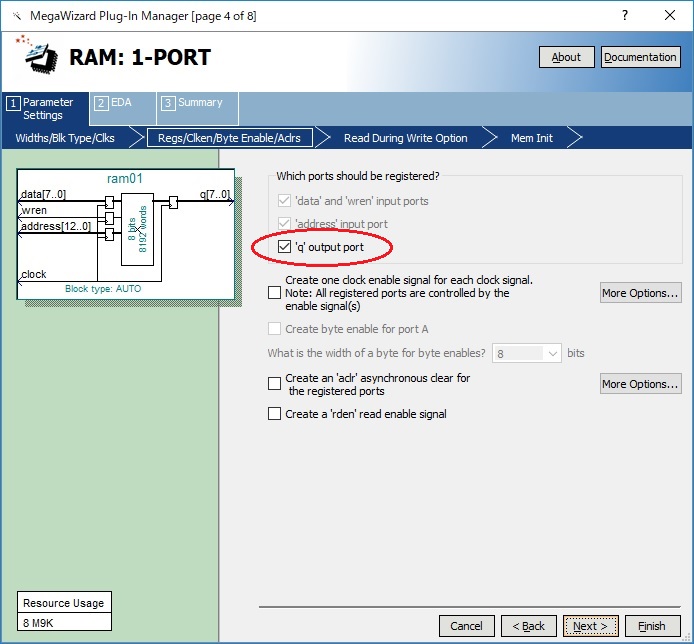

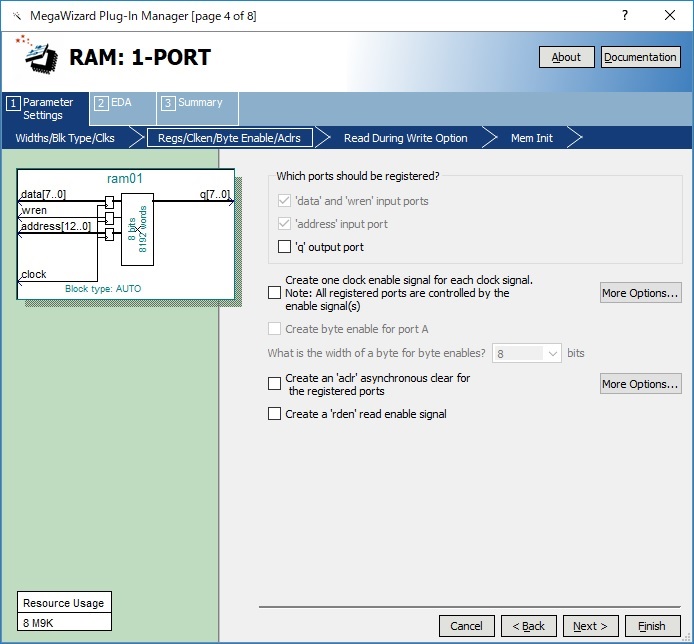

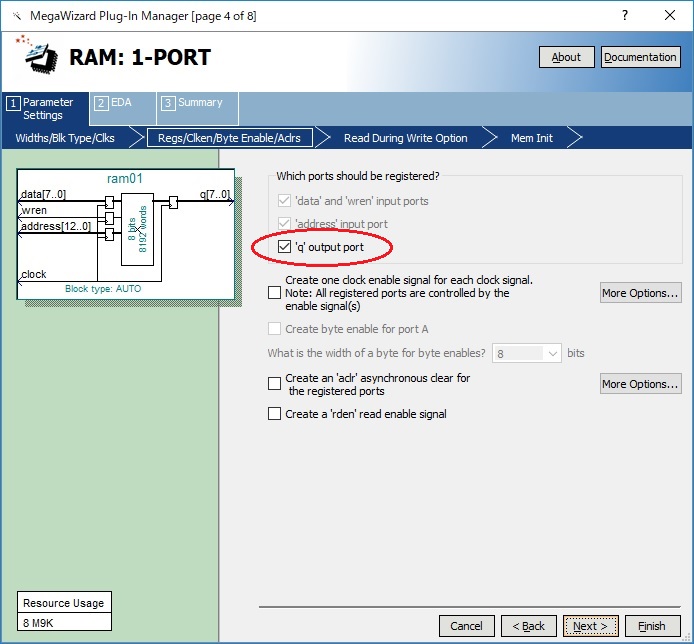

この画面では以下の印を付けた箇所のチェックを外してください。このチェックが入っていると出力端子の値が一度レジスタに記憶されてから出力されてくる仕様になります。(出力端子の値を更新するのにも1クロック必要になります。)

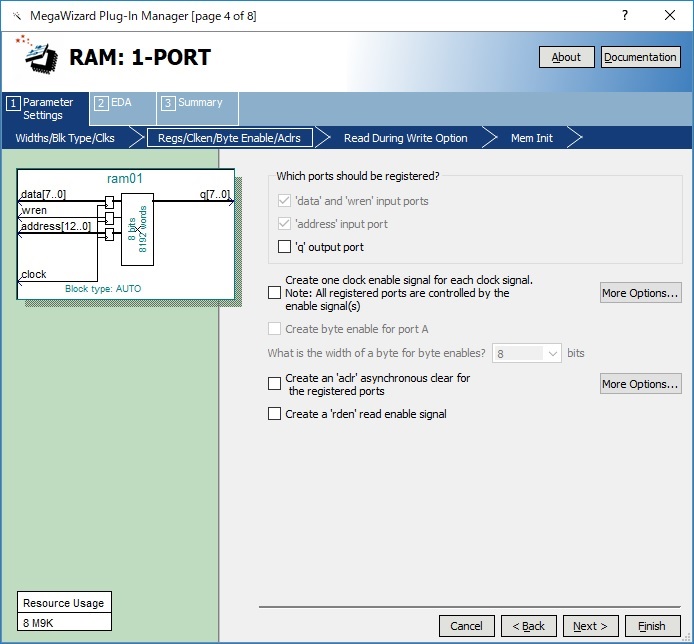

チェックを外すと画面左の回路図も変更され、以下のようになります。(出力端子”q”に付いていたレジスタが無くなっています。)この状態になったら”Next”を押して次へ進みます。

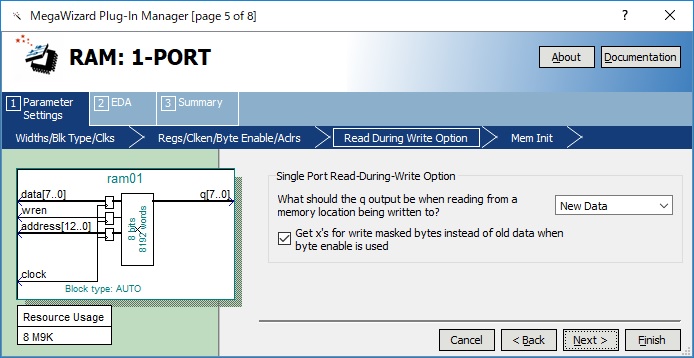

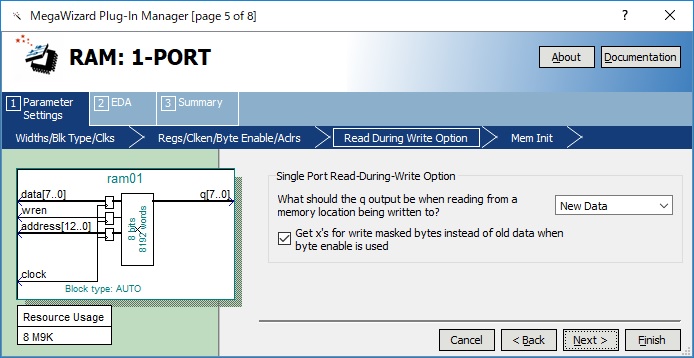

ここでは何もせずに”Next”を押します。

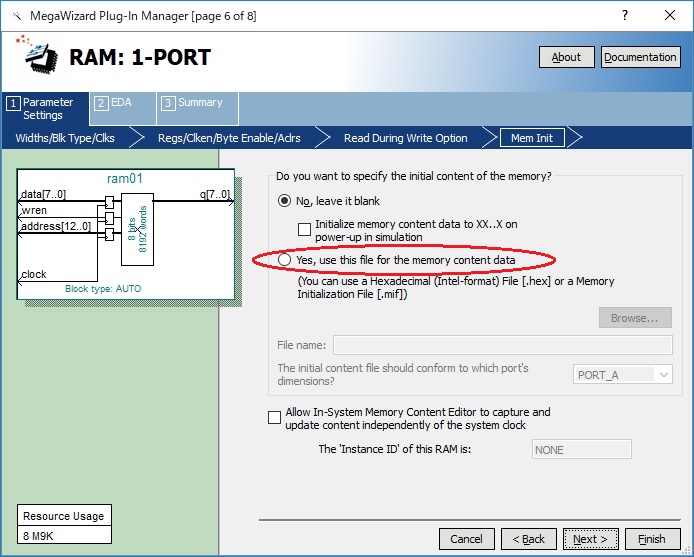

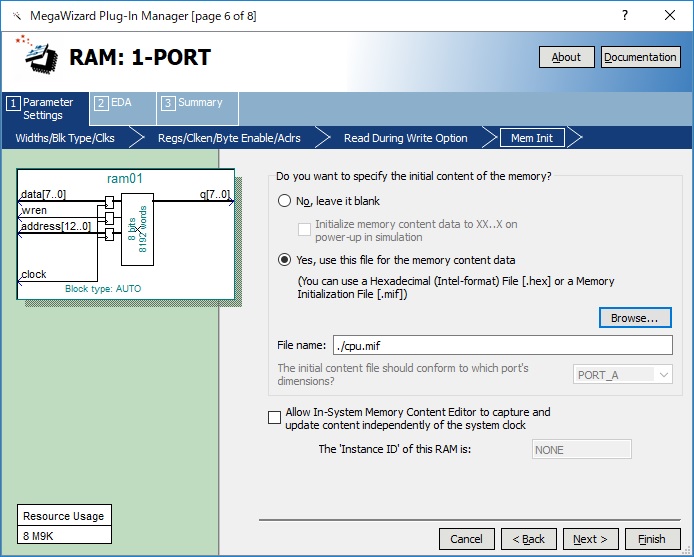

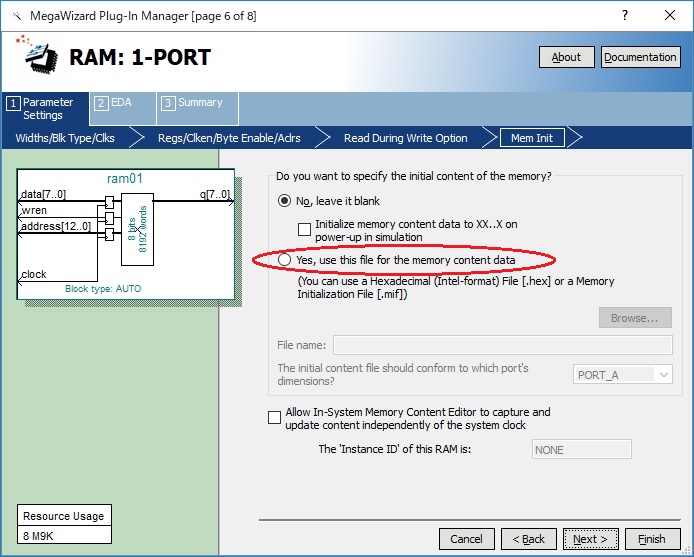

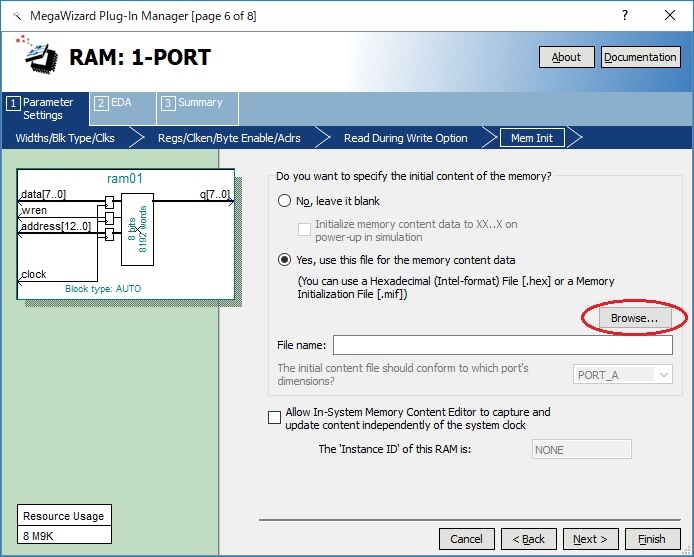

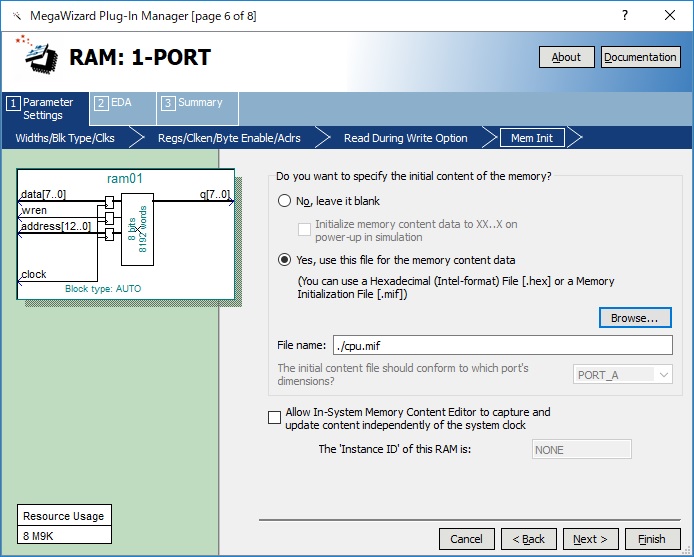

ここではRAMの初期値を指定するMIFファイルの設定をします。以下の印を付けたボタンにチェックを入れます。

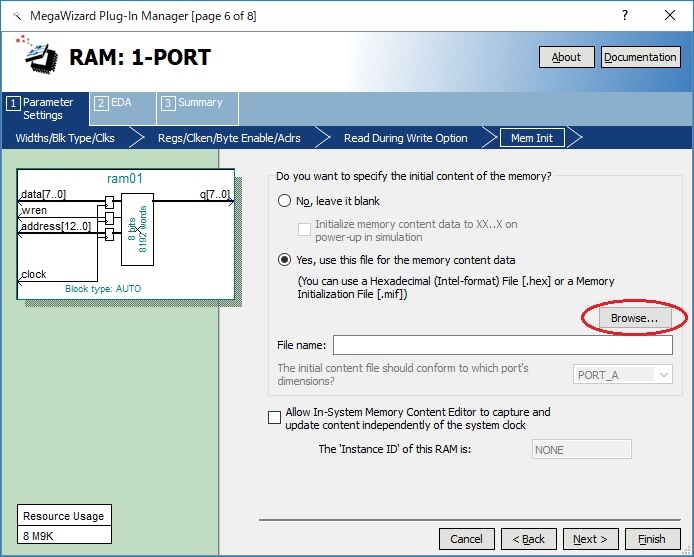

チェックを入れたら”Browse…”ボタンを押します。

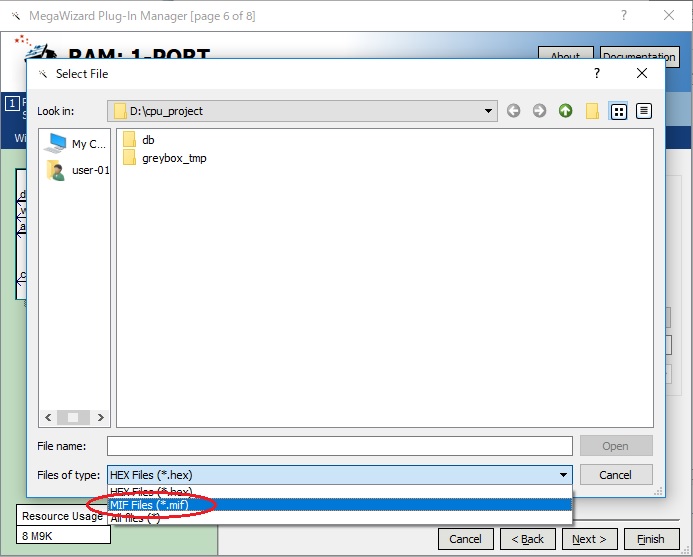

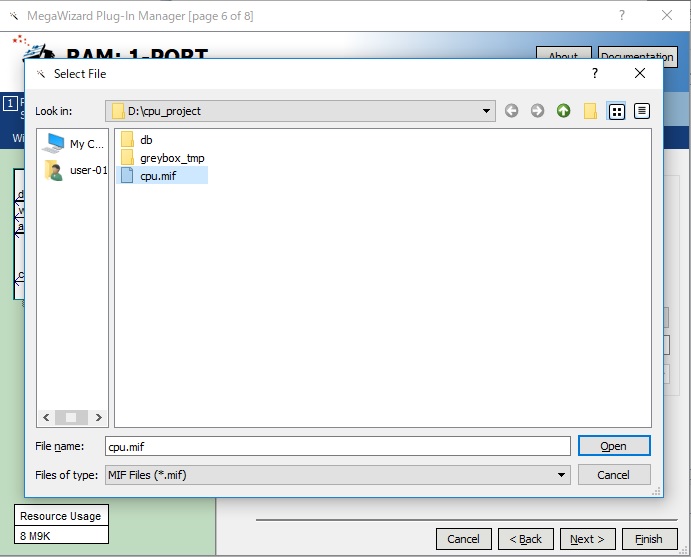

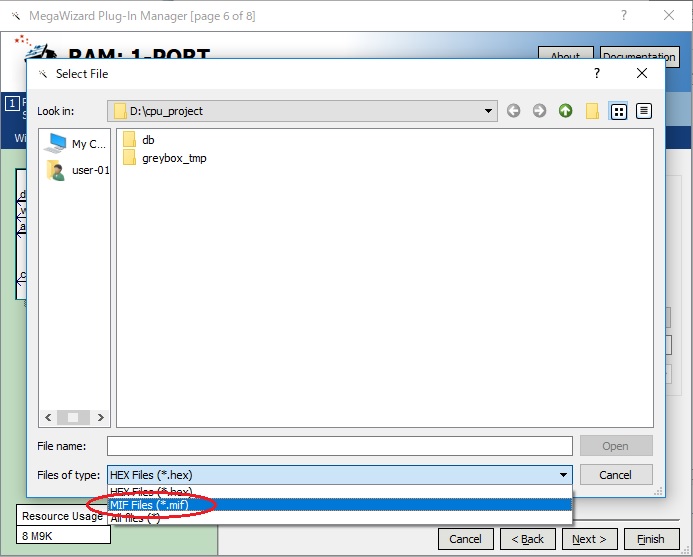

前ページで作成した”cpu.mif”ファイルを選択します。以下のようにしてファイルのタイプを”MIF Files(*.mif)”にしておくと拡張子が”.mif”のタイプのファイルが見えるようになります。

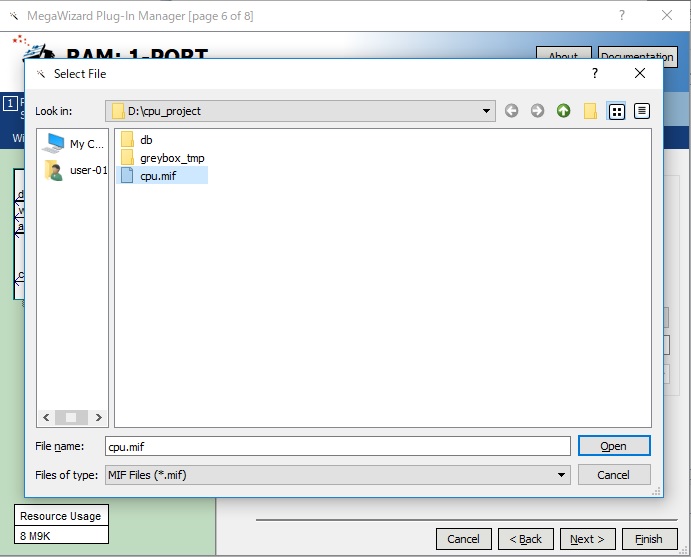

前ページで作成した”cpu.mif”ファイルを選択し、”Open”を押します。

以下のように設定ができたら”Next”を押します。

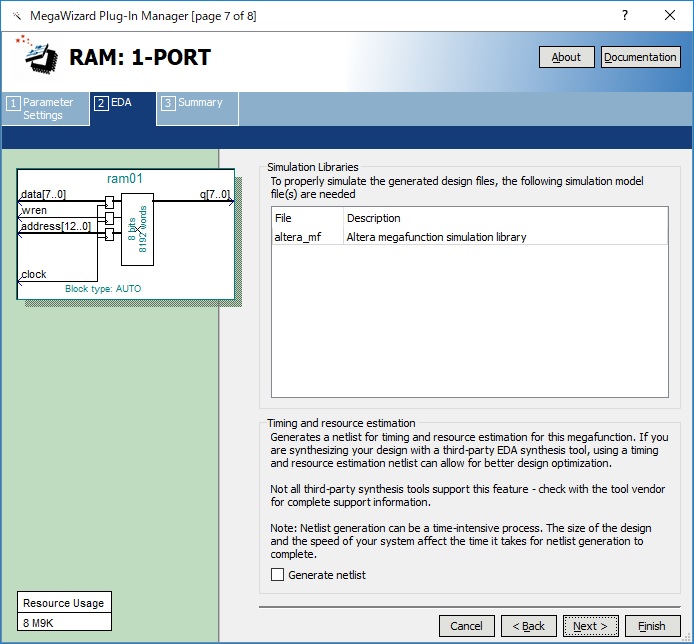

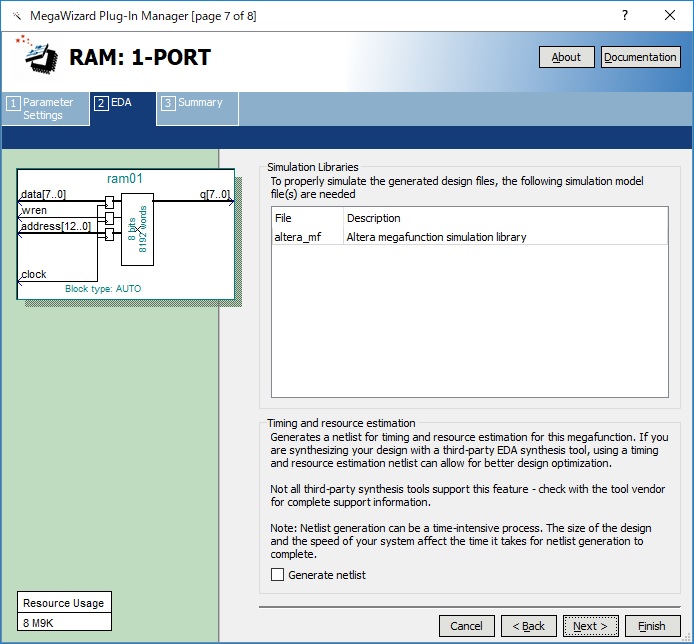

ここでは何もせずに”Next”を押します。

ここも何もせず”Finish”を押して完了です。

<戻る 次へ>